SafeSPI-CTRL – The World’s First Ultra-Flexible SPI Controller IP Core

SafeSPI-CTRL

SafeSPI-CTRL

22.11.2024

Introducing SafeSPI-CTRL – a unique and first of its kind in the global semiconductor market IP core, that sets a new standard in SPI-based communication controllers, designed to meet the stringent requirements of ISO 26262 and automotive ASIL-D applications. As the first IP core of its kind in the world, SafeSPI-CTRL combines unparalleled configurability and flexibility, delivering unique advantages for developers, engineers, and system architects working in the most demanding environments.

Our CEO, Maciej Pyka, calls it ‘ultraflexibility’ – the core’s ability to adapt to multiple roles and configurations, offering solutions that other IP cores simply can’t match.

The Unmatched Flexibility of SafeSPI-CTRL

With SafeSPI-CTRL, you are not locked into a single mode or configuration. Whether you’re developing for a sensor that will function as a Slave, or you need a Master that will autonomously manage communications between peripherals, SafeSPI-CTRL can be tailored to suit your exact application.

SafeSPI-CTRL’s configurability extends beyond just software settings. Developers can make adjustments prior to final silicon production, reducing unnecessary elements and optimizing the core for specific applications. This gives developers the power to create highly efficient, application-specific designs.

Why SafeSPI-CTRL is the Only Choice for Critical Automotive Applications?

With its advanced safety features, support for both 32-bit and 48-bit protocols, autonomous operation, and flexible configuration options, SafeSPI-CTRL is the ideal solution for automotive systems requiring ISO 26262 and ASIL-D compliance. It’s designed to operate efficiently and safely in environments where failure is not an option. Whether you’re working on high-performance communication systems or building safety-critical automotive applications, SafeSPI-CTRL offers the unique combination of flexibility, reliability, and performance that you need.

The SafeSPI-CTRL, developed by Silesia Devices in partnership with CAST, represents a major advancement in SPI communication controllers. This collaborative innovation offers flexibility, safety, and performance for automotive and embedded applications, making it a valuable choice for industry leaders looking to enhance system reliability and resilience.

Key Features

1. Ultimate Configurability and Role Flexibility

SafeSPI-CTRL can be configured to operate in three different modes: Master, Slave or Monitor mode.

This flexibility allows developers to choose the best mode based on the specific application. Whether you’re designing for a sensor acting as a Slave, or configuring an autonomous Master controller that needs to oversee multiple peripherals, SafeSPI-CTRL can be customized to meet your needs.

Moreover, you can lock down configurations before silicon implementation, removing unnecessary components to optimize performance and resource use. Alternatively, the core can be dynamically configured at runtime through software, providing unmatched versatility.

2. Autonomous Operation

One of the most unique features of SafeSPI-CTRL is its ability to work autonomously, operating as an independent bridge without needing continuous processor oversight. Acting as an SPI-to-SafeSPI converter, it can autonomously handle data stream transfers in both directions without processor intervention. This makes it ideal for applications where processor resources are limited or when you need real-time communication without latency.

This autonomous bridge functionality ensures efficient data handling and supports seamless, hardware-level SPI transactions.

3. Support for Multiple SPI Formats

SafeSPI-CTRL supports both 32-bit and 48-bit SPI protocol formats, giving you the flexibility to choose based on your system’s requirements. Whether you’re handling large volumes of data or requiring precision with specific frame sizes, the core is built to accommodate various use cases.

The frame size can also be selected via either a pin or an address mechanism, providing flexibility in how the system interacts with peripherals.

4. Enhanced Data Integrity and Safety Features

Designed in close collaboration with CAST, a leader in functional safety and ISO 26262-compliant IP cores, the SafeSPI-CTRL integrates advanced safety features essential for critical automotive systems. CAST’s experience with ISO 26262 requirements complements Silesia Devices’ technical expertise, resulting in a product optimized for safety-critical applications:

- Automatic CRC (Cyclic Redundancy Check) handling ensures robust data integrity across communication channels.

- Redundancy in critical areas ensures that the system can detect and correct faults, maintaining operational safety even in the face of hardware failures.

- Self-diagnostic capabilities allow external systems to monitor the core’s health, ensuring that any issues are detected early on and addressed promptly. These features are critical for ensuring that the system meets the most stringent functional safety standards.

5. FIFO Depth and Peripheral Handling

SafeSPI-CTRL is built with a customizable FIFO (First-In-First-Out) buffer depth, allowing for efficient data handling. Depending on the system requirements, developers can adjust the FIFO size to optimize throughput and latency.

As a Master, SafeSPI-CTRL supports multiple Slaves, giving developers the ability to connect and manage several peripherals at once. This is particularly useful in complex automotive systems where multiple sensors or devices need to be controlled simultaneously with minimal host processor intervention.

6. Customizable SPI Frame Selection

In some use cases, you may need to adjust the SPI frame size dynamically. SafeSPI-CTRL provides options to select between 32-bit and 48-bit frames using either a pin-based or address-based selection method. This adaptability is essential for systems requiring flexible communication configurations, enhancing the overall system performance and integration.

Introducing the New IP Core in Silesia Devices’ Portfolio

08.04.2024

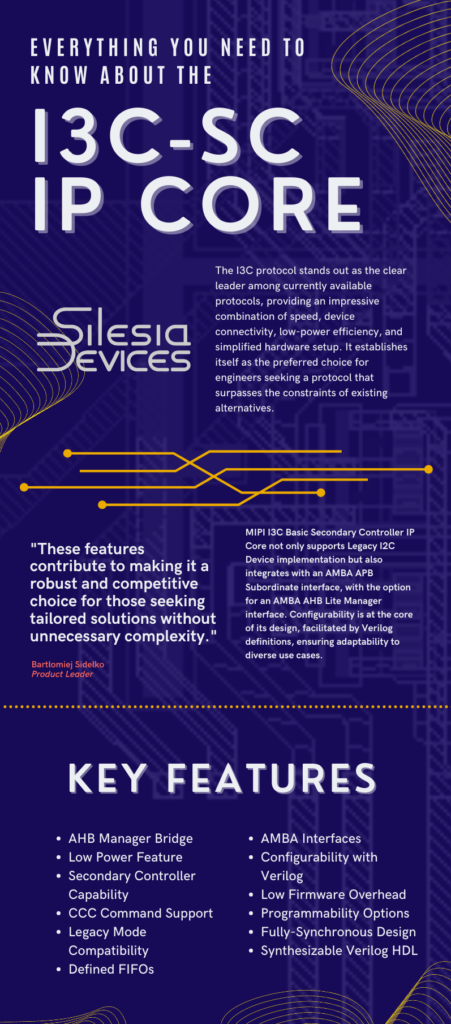

As the demand for seamless connectivity and efficient communication in the IoT ecosystem intensifies, the I3C protocol emerges as an unequivocal frontrunner among the protocols currently available in the market. Offering a compelling synthesis of speed, device connectivity, low-power efficiency, and reduced complexity and intricacies in the hardware setup, the I3C positions itself as the go-to solution for engineers seeking a protocol addressing the limitations of existing alternatives.

That’s why one of our engineering teams spent the last few months creating MIPI I3C Basic Secondary Controller IP Core. This IP core not only implements the most popular subset of the I3C specification, but does it with the maximum possible overhead reduction for the host processor, performing most of the protocol layer operations autonomously. Configurability is at the core of its design, facilitated by Verilog definitions, ensuring adaptability to diverse use cases.

Key attributes that set apart our product from existing IP’s:

1. AHB Manager Bridge:

A distinctive feature allowing the IP Core to act as an AHB Manager Bridge, enabling autonomous data transmission and management. This autonomy streamlines operations, directing traffic through the AHB with minimal host intervention—a unique functionality not standard in I3C.

2. Low Power Feature:

Introduces a low-power mechanism from the AHB perspective. The clock need not operate unless AHB communication is imminent, signaling clock requirements only when data is present in the FIFO—an additional, power-efficient feature.

3. Secondary Controller Capability:

Offers the capability to function as a secondary controller, providing flexibility in managing transmissions as a temporary controller.

4. CCC Command Support:

Implements support for Common Command Codes (CCC), a feature absent in I2C, enhancing command-level functionalities.

5. Legacy Mode Compatibility:

Ensures compatibility with legacy mode I2C in private transmissions, widening the scope of interoperability.

6. Defined FIFOs:

Provides defined FIFOs, alleviating the need for byte-by-byte data handling, enhancing efficiency for the end user.

Technical Insights

The I3C-SC core, compliant with the MIPI I3C BasicSM specification, serves as a versatile secondary controller supporting Single Data Rate (SDR) mode. It seamlessly communicates with legacy I2C devices and can be configured for I3C or I2C bus operation.

Designed for easy integration, the core operates in two modes: normal and I3C-to-AHB bridging. Its highly flexible nature allows synthesis-time and run-time configurations, adapting its size and behavior to application requirements.

The I3C-SC core is available in synthesizable RTL and FPGA netlist forms, equipped with comprehensive support for successful implementation, including Verilog RTL source code, post-synthesis EDIF, testbenches, simulation, synthesis scripts, and documentation.

Our core comes with a warranty against defects for ninety days and thirty days of phone and email technical support from the first interaction. Rigorously verified through synthesis, place and route, simulation runs, and silicon-proven, the I3C-SC core guarantees reliable and trouble-free implementation in ASIC or FPGA technologies.

Explore the future of connectivity with I3C-SC—where innovation meets efficiency in the IoT landscape. Contact CAST inc. to delve into the specifics for your unique application configuration and technology requirements.

MIPI I3C Basic Secondary Controller

From Aspiring to Achieving: Silesia Devices Interns Share Their Stories

10.10.2023

Meet Kamil and Ewelina, two students who joined our summer internship program at Silesia Devices. In this interview, they’ll share their experiences and offer valuable advice for future candidates who may be interested in joining us next year. Get ready to discover what to expect and gain insights into the life at Silesia Devices.

Kamil: I’m Kamil, and I’m currently pursuing a computer science degree at the Silesian University of Technology. Come this fall, I’ll be diving into my third year of studies.

Ewelina: My name is Ewelina, and my academic journey takes place at the same Silesian University of Technology, but my focus is on biomedical engineering. Just like Kamil, I’m gearing up for my third year once the summer break wraps up.

Małgorzata: Let’s dive right into it—how did your adventure start here at Silesia Devices?”

K: I learned about the internship program P4S, led by the Silesian University of Technology, which partners with key businesses in Silesia to foster student development through internship opportunities. I was searching for companies that were involved in areas related to my field of study. Silesia Devices was involved in low-level programming, so I thought it could be a good fit for me. I contacted them, interviewed and got accepted as an intern.

E: I was also searching for an internship, and Silesia Devices was one of the companies that caught my interest. I wanted to develop my programming skills, but I also noticed that the company deals with digital circuits, which my studies didn’t cover extensively. I wanted to explore this area.

M: That’s a bit different from your academic background. Does it also originate from any personal interests or hobbies?

E: My studies are quite diverse, and we learn a little bit of everything. I try to find what suits me best, so I explore various fields.

internship program

Kamil and Ewelina, participants in this year’s last round of recruitment for the internship program at Silesia Devices.

internship program

In 2023, Silesia Devices launched the first edition of its Summer Internship Program. This initiative stems from our commitment to nurturing talent and addressing the decreasing interest in our field among recent graduates. Our internship program is primarily dedicated to students studying in the Department of Automation, Electronics, and Computer Science. However, we wholeheartedly welcome individuals who share a passion for hardware description languages (HDL) design to join us on this exciting journey.

What to Expect

During their internship at Silesia Devices, participants will have the chance to dive headfirst into the world of cutting-edge technology. They will work closely with experienced mentors and actively contribute to ongoing projects, gaining hands-on experience that is invaluable for their career growth.

Interns will also have the opportunity to undertake training projects, providing them with a comprehensive understanding of the practical aspects of the design process. This real-world exposure is an excellent way to bridge the gap between theoretical knowledge and its practical application.

One unique feature of our internship program is the potential to incorporate the practical portion of their thesis into their internship activities. This integration not only enhances their academic pursuits but also allows them to apply their research to real-world projects.

The Road Ahead

Upon successfully completing the internship program, exceptional participants will be considered for future employment opportunities at Silesia Devices. We believe in recognizing and rewarding talent, and our internship program serves as a stepping stone towards a promising career.

M: Kamil, you’re already in your final week of the internship. What were your expectations, and how did the actual experience compare? Could you tell us more about how you’ve adapted here?

K: I wanted to see what working in the profession is like. The atmosphere here is very pleasant, and I don’t feel the typical corporate stress. In fact, it’s been quite the opposite. I found myself gaining not just technical skills but also a deeper appreciation for the friendly atmosphere.

M: I must agree with you. One of the goals when founding the company was to create a friendly and creative work environment that fosters a healthy work-life balance.

K: Yes, I received a lot of support from my colleagues. There were moments when I doubted if this was the right fit for me, but I eventually realized that I could find my place here. The more I learned about FPGA, the more I enjoyed it.

M: Can you pinpoint any specific tasks you’ve worked on during the past three weeks that you found particularly enjoyable?

K: I think working with the electronic evaluation board was the most interesting. It was engaging to have a physical starter kit board in hand and experiment with it. Currently, coding is what I want to pursue professionally, so it is the most satisfying part.

M: Do you see any skills that you’ve acquired here that will be beneficial in your future career?

K: Definitely low-level programming.

E: Also, the opportunity to work in an agile team using scrum methodologies is valuable. Gaining experience in applying these methodologies will be advantageous in the future.

M: Can you share what has surprised you the most during this internship?

Ewelina: I admit I was quite nervous before starting the internship because it’s a specialized company, and I had only basic skills. However, the company considered that and adjusted the internship program accordingly. The longer I work here, the more confident I feel. It’s not as intimidating anymore.

M: Do you believe your majors adequately prepared you for this internship?

E: In my opinion, my major doesn’t fully prepare me for this internship. Our studies cover general basics, but to excel in this field, additional effort and learning are necessary.

K: My major is more closely related to this field. I believe I was well-prepared for this internship. My studies encompass both programming and digital circuits, so I had a theoretical and practical foundation. Now, I can further develop these skills in practice.

M: Are programmable digital circuits something that genuinely interests you after these experiences, or do you view it more as an adventure that will soon come to an end?

K: For me, it’s a very interesting experience. I don’t rule out the possibility of working in this field in the future. I initially chose computer science, focusing on high-level programming, but exploring what we do here has become one of my potential career paths.

E: When I feel more confident after completing the internship, it will be easier to determine whether I want to pursue a career in this industry. Right now, I’m still in the early stages of my learning journey.

M: Do you have any advice for interns who will join our program in 2024?

E: They shouldn’t stress too much. At Silesia Devices, there’s an atmosphere of cooperation and assistance, so they’ll surely manage. However, it would be helpful for future interns to have some basic programming knowledge before they come here.

K: I agree with Ewelina. Without a foundational background, it would be challenging to do meaningful work here. Basic programming and electronics knowledge are definitely important.

M: Thank you, Kamil and Ewelina, for sharing your experiences with us.

With SafeSPI-CTRL, you are not locked into a single mode or configuration. Whether you’re developing for a sensor that will function as a Slave, or you need a Master that will autonomously manage communications between peripherals, SafeSPI-CTRL can be tailored to suit your exact application.

SafeSPI-CTRL’s configurability extends beyond just software settings. Developers can make adjustments prior to final silicon production, reducing unnecessary elements and optimizing the core for specific applications. This gives developers the power to create highly efficient, application-specific designs.